## **Features**

- Bluetooth® v4.1 specification compliant

- Bluetooth Smart

- 128KB memory: 64KB RAM and 64KB ROM

- Support for Bluetooth v4.1 specification host stack including ATT, GATT, SMP, L2CAP, GAP

- RSSI monitoring for proximity applications

- <900nA current consumption in dormant mode</p>

- 32kHz and 16MHz crystal or system clock

- Switch-mode power supply

- Programmable general purpose PIO controller

- 10-bit ADC and a DAC

- 12 digital PIOs

- 1 analogue AIO

- UART

- I<sup>2</sup>C / SPI for EEPROM / flash memory ICs and peripherals

- Debug SPI

- 4 PWM modules

- Wake-up interrupt and watchdog timer

- UT-WLCSP 34-bump, 2.43 x 2.56 x 0.35 mm, 0.4 mm pitch

# **General Description**

CSR1013 WLCSP is a CSR µEnergy platform device. CSR µEnergy are CSR's single-mode Bluetooth low energy products for the Bluetooth Smart market. CSR1013 WLCSP increases application code and data space for greater application development flexibility.

CSR µEnergy enables ultra low-power connectivity and basic data transfer for applications previously limited by the power consumption, size constraints and complexity of other wireless standards. CSR1013 WLCSP provides everything required to create a Bluetooth low energy product with RF, baseband, MCU, qualified Bluetooth v4.1 specification stack and customer application running on a single IC.

# CSR µEnergy® CSR1013 WLCSP

#### Bluetooth Smart IC

**Production Information**

CSR1013A05

Issue 3

# **Applications**

Building an ecosystem using Bluetooth low energy CSR is the industry leader for Bluetooth low energy, also known as Bluetooth Smart. Bluetooth Smart enables connectivity and data transfer to leading smartphone, tablet and personal computing devices including Apple iPhone, iPad, iPod and Mac products and leading Android devices.

Bluetooth low energy takes less time to make a connection than conventional Bluetooth wireless technology and can consume approximately 1/20<sup>th</sup> of the power of Bluetooth Basic Rate. CSR1013 WLCSP supports profiles for health and fitness sensors, watches, keyboards, mice and remote controls.

Typical Bluetooth Smart applications:

- HID: keyboards, mice, touchpads, remote controls

- Sports and fitness sensors: heart rate, runner speed and cadence, cycle speed and cadence

- Health sensors: blood pressure, thermometer and glucose meters

- Mobile accessories: watches, proximity tags, alert tags and camera controls

- Smart home: heating control and lighting control

# **Ordering Information**

|               |                               | Package                               |                    |                   |  |

|---------------|-------------------------------|---------------------------------------|--------------------|-------------------|--|

| Device        | Туре                          | Size                                  | Shipment<br>Method | Order Number      |  |

| CSR1013 WLCSP | UT-WLCSP-34-bump<br>(Pb free) | 2.43 x 2.56 x 0.35 mm<br>0.4 mm pitch | Tape and reel      | CSR1013A05-IUUM-R |  |

#### Note:

Minimum order quantity is 4kpcs taped and reeled.

**Supply chain:** CSR's manufacturing policy is to multisource volume products. For further details, contact your local sales account manager or representative.

# **CSR1013 WLCSP Development Kit Ordering Information**

| Description                                             | Order Number           |

|---------------------------------------------------------|------------------------|

| Starter Development Kit and CSR1013 WLCSP Module Design | See www.csrsupport.com |

### **Contacts**

General information Information on this product Customer support for this product Details of compliance and standards Help with this document www.csr.com sales@csr.com www.csrsupport.com product.compliance@csr.com comments@csr.com

## **Device Details**

#### **Bluetooth Radio**

- On-chip balun (50Ω impedance in TX and RX modes)

- No external trimming is required in production

- Bluetooth v4.1 specification compliant

### **Bluetooth Transmitter**

- 9.0dBm RF transmit power with level control from integrated 6-bit DAC over a dynamic range >25dB

- No external power amplifier or TX/RX switch required

#### **Bluetooth Receiver**

- -91.5dBm sensitivity

- Integrated channel filters

- Digital demodulator for improved sensitivity and cochannel rejection

- Fast AGC for enhanced dynamic range

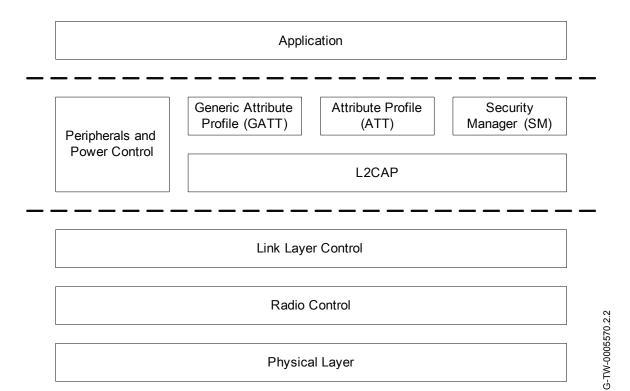

#### **Bluetooth Stack**

CSR's protocol stack runs on the integrated MCU:

- Support for Bluetooth v4.1 specification features:

- Master and slave operation

- Including encryption

- Software stack in firmware includes:

- GAP

- L2CAP

- Security manager

- Attribute protocol

- Attribute profile

- Bluetooth low energy profile support

#### **Synthesiser**

Fully integrated synthesiser requires no external VCO varactor diode, resonator or loop filter

#### **Baseband and Software**

Hardware MAC for all packet types enables packet handling without the need to involve the MCU

#### **Physical Interfaces**

- SPI master interface

- SPI programming and debug interface

- I2C

- 12 digital PIOs

- 1 analogue AIO

- UART

#### **Auxiliary Features**

- Battery monitor

- Power management features include software shutdown and hardware wake-up

- CSR1013 WLCSP can run in low power modes from an external 32.768kHz clock signal

- Integrated switch-mode power supply

- Linear regulator (internal use only)

- Power-on-reset cell detects low supply voltage

#### Package

34-bump 2.43 x 2.56 x 0.35 mm, 0.4 mm pitch UT-WLCSP

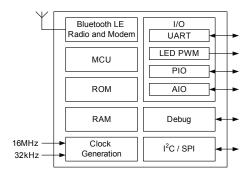

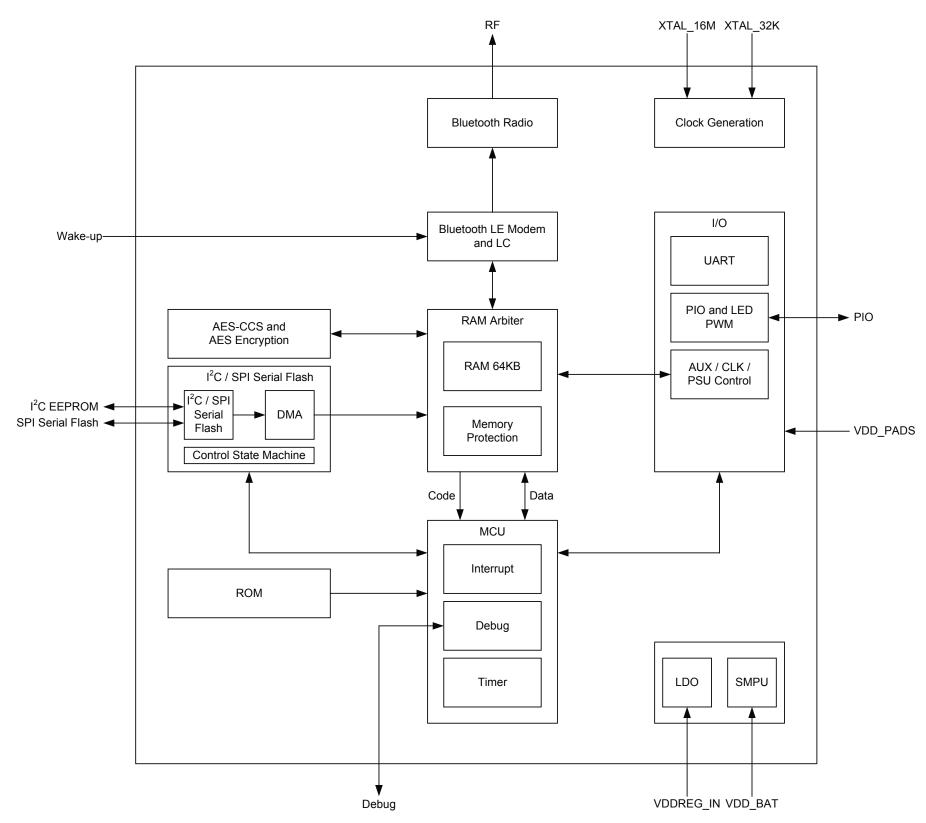

# **Functional Block Diagram**

# **Document History**

| Revision | Date      | Change Reason                          |  |

|----------|-----------|----------------------------------------|--|

| 1        | 14 JAN 15 | Original publication of this document. |  |

| 2        | 15 JAN 15 | Updated Ordering Information.          |  |

| 3        | 19 JUN 15 | Updated to Production Information.     |  |

## Status Information

The status of this Data Sheet is Production Information. CSR Product Data Sheets progress according to the following format:

#### Advance Information:

Information for designers concerning CSR product in development. All values specified are the target values of the design. Minimum and maximum values specified are only given as guidance to the final specification limits and must not be considered as the final values.

#### Engineering Sample:

- Information about initial devices. Devices are untested or partially tested prototypes, their status is described in an Engineering Sample Release Note. All values specified are the target values of the design. Minimum and maximum values specified are only given as guidance to the final specification limits and must not be considered as the final values.

- All detailed specifications including pinouts and electrical specifications may be changed by CSR without notice.

#### Pre-production Information:

- Pinout and mechanical dimension specifications finalised. All values specified are the target values of the design. Minimum

and maximum values specified are only given as guidance to the final specification limits and must not be considered as

the final values.

- All electrical specifications may be changed by CSR without notice.

#### Production Information:

- Final Data Sheet including the guaranteed minimum and maximum limits for the electrical specifications.

- Production Data Sheets supersede all previous document versions.

#### **Device Implementation**

#### Important Note:

As the feature-set of the CSR1013 WLCSP is firmware build-specific, see the relevant software release note for the exact implementation of features on the CSR1013 WLCSP.

#### Life Support Policy and Use in Safety-critical Applications

CSR's products are not authorised for use in life-support or safety-critical applications. Use in such applications is done at the sole discretion of the customer. CSR will not warrant the use of its devices in such applications.

#### CSR Green Semiconductor Products and RoHS Compliance

CSR1013 WLCSP devices meet the requirements of Directive 2011/65/EU of the European Parliament and of the Council on the Restriction of Hazardous Substance (RoHS). CSR1013 WLCSP devices are free from halogenated or antimony trioxide-based flame retardants and other hazardous chemicals. For more information, see CSR's *Environmental Compliance Statement for CSR Green Semiconductor Products*.

#### **Confidentiality Status**

This document is non-confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by CSR plc and the party that CSR plc delivered this document to.

#### Trademarks, Patents and Licences

Unless otherwise stated, words and logos marked with <sup>™</sup> or <sup>®</sup> are trademarks registered or owned by CSR plc or its affiliates. Bluetooth <sup>®</sup> and the Bluetooth <sup>®</sup> logos are trademarks owned by Bluetooth <sup>®</sup> SIG, Inc. and licensed to CSR. Other products, services and names used in this document may have been trademarked by their respective owners.

The publication of this information does not imply that any license is granted under any patent or other rights owned by CSR plc and/or its affiliates.

CSR reserves the right to make technical changes to its products as part of its development programme.

While every care has been taken to ensure the accuracy of the contents of this document, CSR cannot accept responsibility for any errors

Refer to www.csrsupport.com for compliance and conformance to standards information.

# **Contents**

|   | Orde        | ering Information                                  | 2  |  |  |  |  |  |  |

|---|-------------|----------------------------------------------------|----|--|--|--|--|--|--|

|   | O.u.        | CSR1013 WLCSP Development Kit Ordering Information |    |  |  |  |  |  |  |

|   |             | Contacts                                           |    |  |  |  |  |  |  |

|   | Dov         | ice Details                                        |    |  |  |  |  |  |  |

|   |             | ctional Block Diagram                              |    |  |  |  |  |  |  |

| 1 |             | •                                                  |    |  |  |  |  |  |  |

| • |             | Package Information                                |    |  |  |  |  |  |  |

|   | 1.1         | Pinout Diagram                                     |    |  |  |  |  |  |  |

|   | 1.2         | Device Terminal Functions                          |    |  |  |  |  |  |  |

|   | 1.3         | Package Dimensions                                 |    |  |  |  |  |  |  |

|   | 1.4         | PCB Design and Assembly Considerations             |    |  |  |  |  |  |  |

|   | 1.5         | Typical Solder Reflow Profile                      |    |  |  |  |  |  |  |

| 2 |             | etooth Modem                                       |    |  |  |  |  |  |  |

|   | 2.1         | RF Ports                                           |    |  |  |  |  |  |  |

|   | 2.2         | RF Receiver                                        |    |  |  |  |  |  |  |

|   |             | 2.2.1 Low Noise Amplifier                          |    |  |  |  |  |  |  |

|   |             | 2.2.2 RSSI Analogue to Digital Converter           |    |  |  |  |  |  |  |

|   | 2.3         | RF Transmitter                                     |    |  |  |  |  |  |  |

|   |             | 2.3.1 IQ Modulator                                 | 16 |  |  |  |  |  |  |

|   |             | 2.3.2 Power Amplifier                              | 16 |  |  |  |  |  |  |

|   | 2.4         | Bluetooth Radio Synthesiser                        | 16 |  |  |  |  |  |  |

|   | 2.5         | Baseband                                           | 16 |  |  |  |  |  |  |

|   |             | 2.5.1 Physical Layer Hardware Engine               | 16 |  |  |  |  |  |  |

| 3 | Cloc        | ck Generation                                      | 17 |  |  |  |  |  |  |

|   | 3.1         | 3.1 Clock Architecture                             |    |  |  |  |  |  |  |

|   | 3.2         | Crystal Oscillator: XTAL_16M_IN and XTAL_16M_OUT   | 17 |  |  |  |  |  |  |

|   |             | 3.2.1 Crystal Specification                        | 17 |  |  |  |  |  |  |

|   |             | 3.2.2 Frequency Trim                               | 18 |  |  |  |  |  |  |

|   | 3.3         | Sleep Clock                                        | 18 |  |  |  |  |  |  |

|   |             | 3.3.1 Crystal Specification                        |    |  |  |  |  |  |  |

| 4 | Ope         | erating Modes                                      |    |  |  |  |  |  |  |

|   | <b>4</b> .1 | Run Mode                                           |    |  |  |  |  |  |  |

|   | 4.2         | Idle Mode                                          |    |  |  |  |  |  |  |

|   | 4.3         | Deep Sleep Mode                                    |    |  |  |  |  |  |  |

|   | 4.4         | Hibernate Mode                                     |    |  |  |  |  |  |  |

|   | 4.5         | Dormant Mode                                       |    |  |  |  |  |  |  |

| 5 |             | rocontroller, Memory and Baseband Logic            |    |  |  |  |  |  |  |

| Ü | 5.1         | System RAM                                         |    |  |  |  |  |  |  |

|   | 5.2         | Internal ROM                                       |    |  |  |  |  |  |  |

|   | 5.3         | Microcontroller                                    |    |  |  |  |  |  |  |

|   |             |                                                    |    |  |  |  |  |  |  |

|   | 5.4         | Programmable I/O Ports, PIO and AIO                |    |  |  |  |  |  |  |

|   | 5.5         | LED Flasher / PWM Module                           |    |  |  |  |  |  |  |

|   | 5.6         | Temperature Sensor                                 |    |  |  |  |  |  |  |

| _ | 5.7         | Battery Monitor                                    |    |  |  |  |  |  |  |

| 6 |             | al Interfaces                                      |    |  |  |  |  |  |  |

|   | 6.1         | Application Interface                              |    |  |  |  |  |  |  |

|   |             | 6.1.1 UART Interface                               |    |  |  |  |  |  |  |

|   | 6.2         | I <sup>2</sup> C Interface                         |    |  |  |  |  |  |  |

|   | 6.3         | .3 SPI Master Interface                            |    |  |  |  |  |  |  |

|   | 6.4         | Programming and Debug Interface                    | 29 |  |  |  |  |  |  |

|      |         | 6.4.1 Instruction Cycle                                    | 29 |

|------|---------|------------------------------------------------------------|----|

|      |         | 6.4.2 Multi-slave Operation                                | 30 |

| 7    | Powe    | er Control and Regulation                                  | 31 |

|      | 7.1     | Switch-mode Regulator                                      | 31 |

|      | 7.2     | Low-voltage VDD_CORE Linear Regulator                      | 31 |

|      | 7.3     | Reset                                                      | 31 |

|      |         | 7.3.1 Digital Pin States on Reset                          | 31 |

|      |         | 7.3.2 Power-on Reset                                       | 32 |

| 8    | Exam    | nple Application Schematic                                 | 33 |

| 9    | Electi  | trical Characteristics                                     | 34 |

|      | 9.1     | Absolute Maximum Ratings                                   | 34 |

|      | 9.2     | Recommended Operating Conditions                           | 34 |

|      | 9.3     | Input/Output Terminal Characteristics                      | 35 |

|      |         | 9.3.1 Switch-mode Regulator                                | 35 |

|      |         | 9.3.2 Low-voltage Linear Regulator                         | 35 |

|      |         | 9.3.3 Digital Terminals                                    | 35 |

|      |         | 9.3.4 AIO                                                  | 36 |

|      | 9.4     | Junction Temperature                                       | 38 |

|      | 9.5     | ESD Protection                                             | 38 |

| 10   | Curre   | ent Consumption                                            | 39 |

| 11   | CSR     | Green Semiconductor Products and RoHS Compliance           | 40 |

| 12   | CSR1    | 1013 WLCSP Software Stack                                  | 41 |

| 13   | Tape    | and Reel Information                                       | 42 |

|      | 13.1    | Tape Orientation                                           | 42 |

|      | 13.2    | Tape Dimensions                                            | 43 |

|      | 13.3    | Reel Information                                           | 44 |

|      | 13.4    | Moisture Sensitivity Level                                 | 44 |

| 14   | Docu    | ment References                                            | 45 |

| Term | ns and  | Definitions                                                | 46 |

| Lis  | t of    | Figures                                                    |    |

| -    | re 1.1  | Pinout Diagram                                             |    |

| •    | re 3.1  | Clock Architecture                                         |    |

| Figu | re 3.2  | •                                                          |    |

| Figu | re 3.3  | ·                                                          |    |

| •    | re 5.1  | Baseband Digits Block Diagram                              |    |

| _    | re 5.2  |                                                            |    |

| _    | re 6.1  | Example of an I <sup>2</sup> C Interface EEPROM Connection |    |

| _    | re 6.2  |                                                            |    |

| _    | re 6.3  |                                                            |    |

| _    | re 6.4  |                                                            |    |

| -    | re 6.5  |                                                            |    |

| _    | re 7.1  | Voltage Regulator Configuration                            |    |

| _    | re 12.1 |                                                            |    |

| _    | re 13.1 | ·                                                          |    |

| _    | re 13.2 | ·                                                          |    |

| Figu | re 13.3 | 3 Reel Dimensions                                          | 44 |

# **List of Tables**

| Table 3.1  | Crystal Specification                                        | 18 |

|------------|--------------------------------------------------------------|----|

|            |                                                              |    |

| Table 3.2  | Sleep Clock Specification                                    | 19 |

| Table 5.1  | Wake Options for Sleep Modes                                 | 22 |

| Table 5.2  | Alternative PIO Functions                                    |    |

| Table 5.3  | PWM Operating Range                                          | 23 |

| Table 6.1  | Possible UART Settings                                       |    |

| Table 6.2  | I <sup>2</sup> C Standard Mode 100 kHz Timing Definition     | 26 |

| Table 6.3  | I <sup>2</sup> C Fast Mode 400 kHz Timing Definition         | 27 |

| Table 6.4  | SPI Master Serial Flash Memory Interface                     | 28 |

| Table 6.5  | Instruction Cycle for a SPI Transaction                      | 30 |

| Table 7.1  | Pin States on Reset                                          | 32 |

| Table 7.2  | Power-on Reset                                               | 32 |

| Table 9.1  | Junction Temperature within Recommended Operating Conditions | 38 |

| Table 9.2  | ESD Handling Ratings                                         | 38 |

| Table 10.1 | Current Consumption                                          |    |

# 1 Package Information

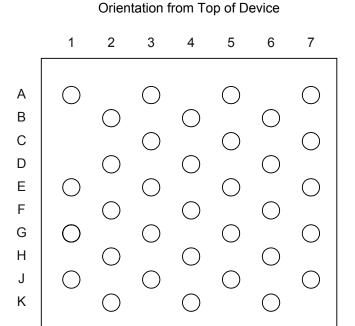

# 1.1 Pinout Diagram

Figure 1.1: Pinout Diagram

G-TW-0014374.2.2

# 1.2 Device Terminal Functions

| Radio | Bump | Pad Type | Supply Domain | Description                       |

|-------|------|----------|---------------|-----------------------------------|

| RF    | D2   | RF       | VDD_REG_IN    | Bluetooth transmitter / receiver. |

| Synthesiser and<br>Oscillator | Bump | Pad Type | Supply Domain | Description                    |

|-------------------------------|------|----------|---------------|--------------------------------|

| XTAL_32K_OUT                  | H2   | Analogue | VDD_BAT       | Drive for sleep clock crystal. |

| XTAL_32K_IN                   | J1   | Analogue | VDD_BAT       | 32.768kHz sleep clock input.   |

| XTAL_16M_OUT                  | B2   | Analogue | VDD_XTAL      | Drive for crystal.             |

| XTAL_16M_IN                   | А3   | Analogue | VDD_XTAL      | Reference clock input.         |

| I <sup>2</sup> C Interface | Bump | Pad Type                                                  | Supply Domain | Description                                                                                                                                                    |

|----------------------------|------|-----------------------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I2C_SDA                    | J5   | Bidirectional, tristate,<br>with weak internal<br>pull-up | VDD_PADS      | I <sup>2</sup> C data input / output or SPI serial flash data output (SF_DOUT). If connecting to SPI serial flash, connect this pin to SO on the serial flash. |

| I2C_SCL                    | G5   | Input with weak internal pull-up                          | VDD_PADS      | I <sup>2</sup> C clock or SPI serial flash clock output (SF_CLK).                                                                                              |

| PIO Port               | Bump | Pad Type                                           | Supply Domain | Description                                                                |

|------------------------|------|----------------------------------------------------|---------------|----------------------------------------------------------------------------|

| PIO[11]                | E3   | Bidirectional with                                 |               |                                                                            |

| PIO[10]                | D4   | programmable strength internal pull-               | VDD_PADS      | Programmable I/O line.                                                     |

| PIO[9]                 | J7   | up/down                                            |               |                                                                            |

| PIO[8] /<br>DEBUG_MISO | F6   |                                                    | VDD_PADS      | Programmable I/O line or debug SPI MISO selected by SPI_PIO#.              |

| PIO[7] /<br>DEBUG_MOSI | E7   | Bidirectional with                                 |               | Programmable I/O line or debug SPI MOSI selected by SPI_PIO#.              |

| PIO[6] /<br>DEBUG_CS#  | C7   | programmable<br>strength internal pull-<br>up/down |               | Programmable I/O line or debug SPI chip select (CS#) selected by SPI_PIO#. |

| PIO[5] /<br>DEBUG_CLK  | D6   |                                                    |               | Programmable I/O line or debug SPI CLK selected by SPI_PIO#.               |

| PIO Port            | Bump | Pad Type                                                       | Supply Domain | Description                                                                                                                                    |

|---------------------|------|----------------------------------------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO[4] /<br>SF_CS#  | A7   | Bidirectional with                                             |               | Programmable I/O line or SPI serial flash chip select (SF_CS#).                                                                                |

| PIO[3] /<br>SF_DIN  | В6   | programmable<br>strength internal pull-<br>up/down             | VDD_PADS      | Programmable I/O line or SPI serial flash data (SF_DIN) input. If connecting to SPI serial flash, this pin connects to SI on the serial flash. |

| PIO[2]              | H6   | Bidirectional with programmable strength internal pull-up/down | VDD_PADS      | Programmable I/O line or I <sup>2</sup> C power.                                                                                               |

| PIO[1] /<br>UART_RX | C5   | Bidirectional with programmable                                | VDD_PADS      | Programmable I/O line or UART RX.                                                                                                              |

| PIO[0] /<br>UART_TX | A5   | strength internal pull-<br>up/down                             |               | Programmable I/O line or UART TX.                                                                                                              |

| AIO[0]              | B4   | Bidirectional analogue                                         | VDD_XTAL      | Analogue programmable I/O line.                                                                                                                |

| Test and Debug | Bump | Pad Type                             | Supply Domain | Description                    |

|----------------|------|--------------------------------------|---------------|--------------------------------|

| SPI_PIO#       | K6   | Input with strong internal pull-down | VDD_PADS      | Selects SPI debug on PIO[8:5]. |

| Wake-up | Bump | Pad Type                                                            | Supply Domain | Description                                            |

|---------|------|---------------------------------------------------------------------|---------------|--------------------------------------------------------|

| WAKE    | F2   | Input has no internal pull-up or pull-down, use external pull-down. | VDD_BAT       | Input to wake CSR1013 WLCSP from hibernate or dormant. |

| Power Supplies and Control | Bump | Description                                          |  |  |

|----------------------------|------|------------------------------------------------------|--|--|

| VDD_BAT                    | G3   | Battery input and regulator enable (active high).    |  |  |

| VDD_BAT_SMPS               | J3   | Input to high-voltage switch-mode regulator.         |  |  |

| SMPS_LX                    | K2   | High-voltage switch-mode regulator output.           |  |  |

| VDD_CORE                   | K4   | Positive supply for digital domain.                  |  |  |

| VDD_PADS                   | G7   | Positive supply for all digital I/O ports PIO[11:0]. |  |  |

| Power Supplies and<br>Control | Bump   | Description                                                       |

|-------------------------------|--------|-------------------------------------------------------------------|

| VDD_REG_IN                    | G1     | Positive supply for Bluetooth radio and digital linear regulator. |

| VDD_XTAL                      | A1     | Decouple with 470nF capacitor to ground.                          |

| VSS_AUX_LO                    | C3     | Ground for AUX and LO.                                            |

| VSS_DIG                       | E5, F4 | Digital ground.                                                   |

| VSS_RADIO                     | E1     | RF ground.                                                        |

| VSS_VBAT_SMPS                 | H4     | Switcher ground.                                                  |

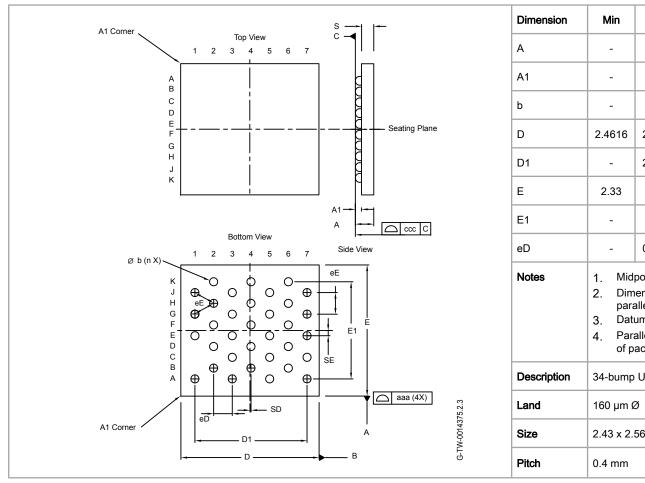

# 1.3 Package Dimensions

| Dimension   | Min                                                                                                                                                                                                                                                                                                                                             | Тур    | Max    | Dimension | Min | Тур   | Max |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|-----------|-----|-------|-----|

| А           | -                                                                                                                                                                                                                                                                                                                                               | 0.335  | 0.35   | еE        | -   | 0.4   | -   |

| A1          | -                                                                                                                                                                                                                                                                                                                                               | 0.11   | -      | n         | -   | 34    | -   |

| b           | -                                                                                                                                                                                                                                                                                                                                               | 0.17   | -      | s         | -   | 0.225 | -   |

| D           | 2.4616                                                                                                                                                                                                                                                                                                                                          | 2.5116 | 2.5616 | SD        | -   | 0.02  | -   |

| D1          | -                                                                                                                                                                                                                                                                                                                                               | 2.0784 | -      | SE        | -   | 0.1   | -   |

| E           | 2.33                                                                                                                                                                                                                                                                                                                                            | 2.380  | 2.43   | aaa       | -   | 0.05  | -   |

| E1          | -                                                                                                                                                                                                                                                                                                                                               | 1.8    | -      | ccc       | -   | 0.08  | -   |

| eD          | -                                                                                                                                                                                                                                                                                                                                               | 0.3464 | -      | -         | -   | -     | -   |

| Notes       | <ol> <li>Midpoint of bump array is offset to centre of component.</li> <li>Dimension b is measured at the maximum solder bump diameter parallel to datum plane C.</li> <li>Datum C is defined by the spherical crowns of the solder bumps.</li> <li>Parallel measurement shall exclude any effect of mark on top surface of package.</li> </ol> |        |        |           |     |       |     |

| Description | 34-bump Ultra-thin Wafer-level Chip-scale Package (UT-WLCSP)                                                                                                                                                                                                                                                                                    |        |        |           |     |       |     |

| Land        | 160 µm Ø                                                                                                                                                                                                                                                                                                                                        |        |        |           |     |       |     |

| Size        | 2.43 x 2.56 x 0.35 mm <b>JEDEC</b> Non-JEDEC                                                                                                                                                                                                                                                                                                    |        |        |           | EC  |       |     |

| Pitch       | 0.4 mm Units mm                                                                                                                                                                                                                                                                                                                                 |        |        |           |     |       |     |

## 1.4 PCB Design and Assembly Considerations

This section lists recommendations to achieve maximum board-level reliability of the 2.43 x 2.56 x 0.35 mm UT-WLCSP 34-bump package:

- NSMD lands (that is, lands smaller than the solder mask aperture) are preferred because of the greater accuracy of the metal definition process compared to the solder mask process. With solder mask defined pads, the overlap of the solder mask on the land creates a step in the solder at the land interface, which can cause stress concentration and act as a point for crack initiation.

- Ideally, via-in-pad technology should be used to achieve truly NSMD lands. Where this is not possible, a maximum of one trace connected to each land is preferred. This trace should be as thin as possible, taking into consideration its current carrying and the RF requirements.

- CSR recommends 35µm thick (1oz) copper lands rather than 17µm thick (0.5oz). This results in a greater standoff which has been proven to provide greater reliability during thermal cycling.

- Land diameter should be 160 µm ±10µm to achieve optimum reliability.

- UT-WLCSP parts have nominal bump geometries of 100µm (height) and 160µm (diameter). To maintain the lowest profile solution, CSR recommends a flux-only assembly process.

- UT-WLCSP can be mounted using a solder paste assembly process. However because additional solder material is introduced, the final bump height will be higher. An increase in the final volume of solder in the joint generally increases reliability.

- Differences in CTE ratings between UT-WLCSP (silicon) and application substrate should be carefully considered.

- Reliability may be enhanced by the introduction of a suitable underfill material.

- Where possible, the solder lands should be finished with OSP.

- Where a nickel gold plating finish is used, the gold thickness should be kept below 0.5μm to prevent brittle gold/tin intermetallics forming in the solder.

- The UT-WLCSP is designed so that bump lands do not lie on top of sensitive areas of the active silicon.

- UT-WLCSP components often have the bump array mid-point offset to the centre of the component outline.

This requires careful consideration during component footprint design.

UT-WLCSP devices have proven to be reliable. However, by their nature they are more susceptible to handling damage than plastic packaged devices. Care should be taken to optimise placement equipment settings for UT-WLCSPs, and care should be taken when handling PCBs with UT-WLCSPs attached.

# 1.5 Typical Solder Reflow Profile

For information, see Typical Solder Reflow Profile for Lead-free Devices Information Note.

# 2 Bluetooth Modem

### 2.1 RF Ports

CSR1013 WLCSP contains an integrated balun which provides a single-ended RF TX / RX port pin. No matching components are needed as the receive mode impedance is  $50\Omega$  and the transmitter has been optimised to deliver power in to a  $50\Omega$  load.

### 2.2 RF Receiver

The receiver features a near-zero IF architecture that allows the channel filters to be integrated onto the die. Sufficient out-of-band blocking specification at the LNA input allows the receiver to be used in close proximity to GSM and W-CDMA cellular phone transmitters without being significantly desensitised.

An ADC digitises the IF received signal.

### 2.2.1 Low Noise Amplifier

The LNA operates in differential mode and takes its input from the balanced port of the integrated balun.

### 2.2.2 RSSI Analogue to Digital Converter

The ADC samples the RSSI voltage on a packet-by-packet basis and implements a fast AGC. The front-end LNA gain is changed according to the measured RSSI value, keeping the first mixer input signal within a limited range. This improves the dynamic range of the receiver, improving performance in interference-limited environments.

### 2.3 RF Transmitter

#### 2.3.1 IQ Modulator

The transmitter features a direct IQ modulator to minimise frequency drift during a transmit packet, which results in a controlled modulation index. Digital baseband transmit circuitry provides the required spectral shaping.

#### 2.3.2 Power Amplifier

The internal PA has a maximum 9.0dBm output power without needing an external RF PA.

# 2.4 Bluetooth Radio Synthesiser

The Bluetooth radio synthesiser is fully integrated onto the die with no requirement for an external VCO screening can, varactor tuning diodes, LC resonators or loop filter. The synthesiser is guaranteed to lock in sufficient time across the guaranteed temperature range to meet the Bluetooth v4.1 specification.

### 2.5 Baseband

## 2.5.1 Physical Layer Hardware Engine

Dedicated logic performs:

- Cyclic redundancy check

- Encryption

- Data whitening

- Access code correlation

The hardware supports all optional and mandatory features of Bluetooth v4.1 specification.

3-TW-0005266.2.2

G-TW-0005348.1.1

## 3 Clock Generation

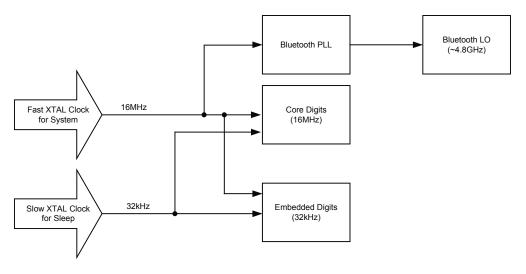

The Bluetooth reference clock for the system is generated from an external 16MHz clock source, see Figure 3.1. All the CSR1013 WLCSP internal digital clocks are generated using a phase locked loop, which is locked to the frequency of either the external reference clock source or a sleep clock frequency of 32.768kHz, see Figure 3.1.

## 3.1 Clock Architecture

Figure 3.1: Clock Architecture

# 3.2 Crystal Oscillator: XTAL\_16M\_IN and XTAL\_16M\_OUT

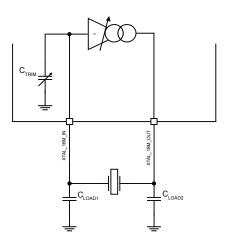

CSR1013 WLCSP contains crystal driver circuits. This operates with an external crystal and capacitors to form a Pierce oscillator. Figure 3.2 shows the external crystal is connected to pins XTAL\_16M\_IN and XTAL\_16M\_OUT.

Figure 3.2: Crystal Driver Circuit

#### Note:

C<sub>TRIM</sub> is the internal trimmable capacitance in Table 3.1.

$C_{\text{LOAD1}}$  and  $C_{\text{LOAD2}}$  in combination with  $C_{\text{TRIM}}$  and any parasitic capacitance provide the load capacitance required by the crystal.

### 3.2.1 Crystal Specification

Table 3.1 shows the specification for an external crystal.

| Parameter                                             | Min | Тур | Max | Unit   |

|-------------------------------------------------------|-----|-----|-----|--------|

| Frequency                                             | -   | 16  | -   | MHz    |

| Frequency tolerance (without trimming) <sup>(a)</sup> | -   | -   | ±25 | ppm    |

| Frequency trim range <sup>(b)</sup>                   | -   | ±50 | -   | ppm    |

| Drive level                                           | -   | 0.4 | -   | V      |

| Equivalent series resistance                          | -   | -   | 60  | Ω      |

| Load capacitance                                      | -   | 9   | -   | pF     |

| Pullability                                           | 10  | -   | -   | ppm/pF |

Table 3.1: Crystal Specification

## 3.2.2 Frequency Trim

CSR1013 WLCSP contains variable integrated capacitors to allow for fine-tuning of the crystal resonant frequency. This firmware-programmable feature allows accurate trimming of crystals on a per-device basis on the production line. The resulting trim value is stored in non-volatile memory.

# 3.3 Sleep Clock

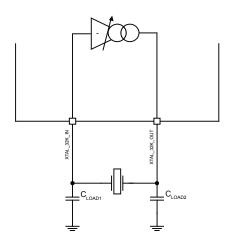

The sleep clock is an externally provided 32.768kHz clock that is used during deep sleep and in other low-power modes. Figure 3.3 shows the sleep clock crystal driver circuit.

Figure 3.3: Sleep Clock Crystal Driver Circuit

#### Note:

$C_{\text{LOAD1}}$  and  $C_{\text{LOAD2}}$  in combination with any parasitic capacitance provide the load capacitance required by the crystal.

### 3.3.1 Crystal Specification

Table 3.2 shows the requirements for the sleep clock.

<sup>(</sup>a) Use integrated load capacitors to trim initial frequency tolerance in production or to trim frequency over temperature, increasing the allowable frequency tolerance.

<sup>(</sup>b) Frequency trim range is dependent on crystal load capacitor values and crystal pullability.

| Sleep Clock                            | Min   | Тур    | Max   | Units |

|----------------------------------------|-------|--------|-------|-------|

| Frequency                              | 30    | 32.768 | 35    | kHz   |

| Frequency tolerance <sup>(a) (b)</sup> | -     | -      | 250   | ±ppm  |

| Frequency trim range                   | -     | 50     | -     | ±ppm  |

| Drive level                            | -     | 0.4    | -     | V     |

| Load capacitance                       | -     | -      | 10    | pF    |

| Equivalent series resistance           | 40    | -      | 65    | kΩ    |

| Duty cycle                             | 30:70 | 50:50  | 70:30 | %     |

#### Table 3.2: Sleep Clock Specification

<sup>(</sup>a) The frequency of the slow clock is periodically calibrated against the system clock. As a result the rate of change of the frequency is more important than the maximum deviation. To meet the accuracy requirements the frequency should not drift due to temperature or other effects by more than 80ppm in any 5 minute period.

<sup>(</sup>b) CSR1013 WLCSP can correct for ±1% by using the fast clock to calibrate the slow clock.

# 4 Operating Modes

CSR1013 WLCSP has 5 operating modes. 3 of these are sleep modes:

- Running

- Idle

- Sleep modes:

- Deep Sleep

- Hibernate

- Dormant

For current consumption rates in the operating modes, see Section 10.

### 4.1 Run Mode

In Run mode, all functions are on. RX and/or TX are active.

### 4.2 Idle Mode

In Idle mode, the VDD\_PADS and VDD\_BAT domains are powered, the reference clock and the sleep clock are powered, the RAM is powered and the digital circuits are powered. The MCU is idle.

There is a <1µs wake-up time.

## 4.3 Deep Sleep Mode

In Deep Sleep mode, the VDD\_PADS and VDD\_BAT domains are powered, the sleep clock is on but the reference clock is off, the RAM is on, the digital circuits are on and the SMPS is on (low-power mode). There is a configurable wake-up time.

CSR1013 WLCSP is woken from Deep Sleep mode by any PIO configured to wake the IC.

### 4.4 Hibernate Mode

In Hibernate mode, the VDD\_PADS and VDD\_BAT domains are powered and the sleep clock is on. The reference clock is off.

CSR1013 WLCSP is woken from Hibernate mode by a selected level on the WAKE pin or by the watchdog timer.

### 4.5 Dormant Mode

In Dormant mode, all functions are off. CSR1013 WLCSP is woken from Dormant mode by a selected level on the WAKE pin.

G-TW-0005354.3.2

# 5 Microcontroller, Memory and Baseband Logic

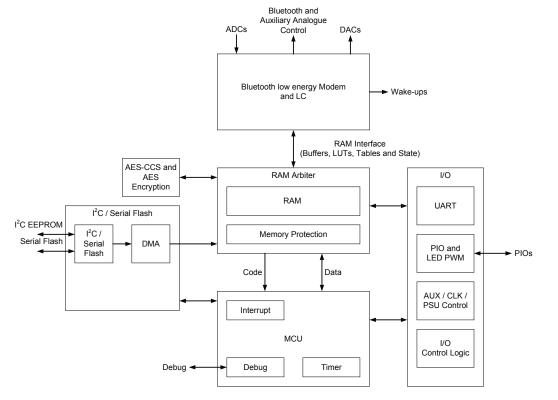

Figure 5.1: Baseband Digits Block Diagram

# 5.1 System RAM

64KB of integrated RAM supports the RISC MCU and is shared between the ring buffers used to hold data for each active connection, general-purpose memory required by the Bluetooth stack and the user application.

### 5.2 Internal ROM

CSR1013 WLCSP has 64KB of internal ROM. This memory is provided for system firmware implementation. If the internal ROM holds valid program code, on boot-up, this is copied into the program RAM. Code then executes from ROM and RAM.

#### 5.3 Microcontroller

The MCU, interrupt controller and event timer run the Bluetooth software stack and control the Bluetooth radio and external interfaces. A 16-bit RISC microcontroller is used for low power consumption and efficient use of memory.

# 5.4 Programmable I/O Ports, PIO and AIO

12 lines of programmable bidirectional I/O are provided. They are all powered from VDD PADS.

PIO lines are software-configurable as weak pull-up, weak pull-down, strong pull-up or strong pull-down.

#### Note:

At reset all PIO lines are inputs with weak pull-downs.

Any of the PIO lines can be configured as interrupt request lines or to wake the IC from deep sleep mode. Table 5.1 lists the options for waking the IC from the sleep modes.

| Sleep Mode | Wake-up Options                                        |

|------------|--------------------------------------------------------|

| Dormant    | Can only be woken by the WAKE pin.                     |

| Hibernate  | Can be woken by the WAKE pin or by the watchdog timer. |

| Deep Sleep | Can be woken by any PIO configured to wake the IC.     |

#### Table 5.1: Wake Options for Sleep Modes

The CSR1013 WLCSP supports alternative functions on the PIO lines, for example:

- SPI interface, see Section 1.2 and Section 6.4

- UART, see Section 1.2 and Section 6.1.1

- LED flasher / PWM module, see Section 5.5

Table 5.2 shows the alternative functions on the PIO lines.

| DIO    | Function   |           |         |  |  |

|--------|------------|-----------|---------|--|--|

| PIO    | Debug SPI  | SPI Flash | UART    |  |  |

| PIO[8] | DEBUG_MISO | -         | -       |  |  |

| PIO[7] | DEBUG_MOSI | -         | -       |  |  |

| PIO[6] | DEBUG_CS#  | -         | -       |  |  |

| PIO[5] | DEBUG_CLK  | -         | -       |  |  |

| PIO[4] | -          | SF_CS#    | -       |  |  |

| PIO[3] | -          | SF_DIN    | -       |  |  |

| PIO[2] | -          | -         | -       |  |  |

| PIO[1] | -          | -         | UART_RX |  |  |

| PIO[0] | -          | -         | UART_TX |  |  |

Table 5.2: Alternative PIO Functions

#### Note:

CSR cannot guarantee that the PIO assignments remain as described. Implementation of the PIO lines is firmware build-specific, for more information see the relevant software release note.

CSR1013 WLCSP has 1 general-purpose analogue interface pins, AIO[0].

### 5.5 LED Flasher / PWM Module

CSR1013 WLCSP contains an LED flasher / PWM module.

#### Note:

The LED flasher functions in Deep Sleep and Active modes only.

The PWM functions in all modes except Hibernate and Dormant.

These functions are controlled by the on-chip firmware.

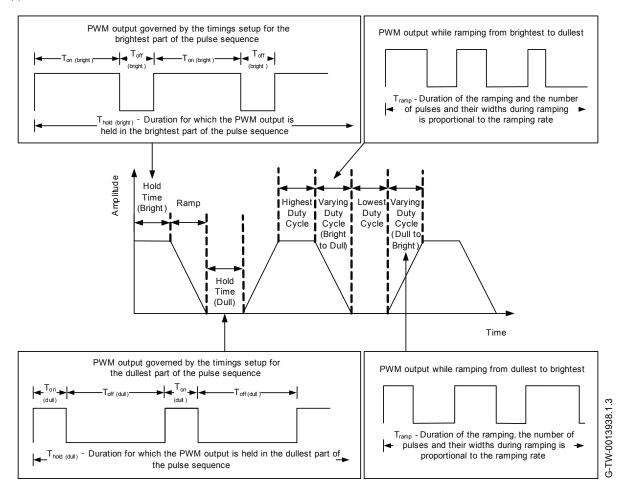

Figure 5.2 shows a typical PWM signal on a PIO. For more information, see *CSR* µEnergy Pulse Width Modulation Application Note.

Figure 5.2: Typical PWM Signal on a PIO

Figure 5.2 lists PWM the operating range.

| Parameter                                                              | Min  | Max   | Unit |

|------------------------------------------------------------------------|------|-------|------|

| Off Time (T <sub>off</sub> )                                           | 30.5 | 7782  | μs   |

| On Time (T <sub>on</sub> )                                             | 30.5 | 7782  | μs   |

| Hold Time (T <sub>hold</sub> )                                         | 16   | 4080  | ms   |

| Duty Cycle = On Time (T <sub>on</sub> ) + Off Time (T <sub>off</sub> ) | 61   | 15564 | μs   |

| Frequency = 1 / Duty Cycle                                             | 64.3 | 16320 | Hz   |

Table 5.3: PWM Operating Range

# 5.6 Temperature Sensor

CSR1013 WLCSP contains a temperature sensor that measures the temperature of the die to an accuracy of ±1 °C.

# 5.7 Battery Monitor

CSR1013 WLCSP contains an internal battery monitor that reports the battery voltage to the software.

## 6 Serial Interfaces

# 6.1 Application Interface

#### 6.1.1 UART Interface

The CSR1013 WLCSP UART interface provides a simple mechanism for communicating with other serial devices using the RS232 protocol.

2 signals implement the UART function, UART\_TX and UART\_RX. When CSR1013 WLCSP is connected to another digital device, UART\_RX and UART\_TX transfer data between the 2 devices.

UART configuration parameters, e.g. baud rate and data format, are set using CSR1013 WLCSP firmware.

When selected in firmware PIO[0] is assigned to a UART\_TX output and PIO[1] is assigned to a UART\_RX input, see Section 1.2.

#### Note:

To communicate with the UART at its maximum data rate using a standard PC, the PC requires an accelerated serial port adapter card.

Table 6.1 shows the possible UART settings for the CSR1013 WLCSP.

| Parameter           |          | Possible Values        |

|---------------------|----------|------------------------|

| Doud rate           | Minimum  | 2400 baud (≤2%Error)   |

| Baud rate           | Wilnimum | 9600 baud (≤2%Error)   |

| Maximum             |          | 3.69Mbaud (≤0.1%Error) |

| Parity              |          | None, Odd or Even      |

| Number of stop bits |          | 1 or 2                 |

| Bits per byte       |          | 8                      |

Table 6.1: Possible UART Settings

#### 6.1.1.1 UART Configuration While in Deep Sleep

The maximum baud rate is 2400 baud during deep sleep.

### 6.2 I<sup>2</sup>C Interface

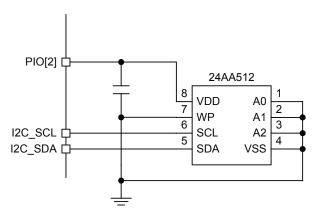

The I<sup>2</sup>C interface communicates to EEPROM, external peripherals or sensors. An external EEPROM connection can hold the program code externally to the CSR1013 WLCSP.

Figure 6.1 shows an example of an EEPROM connected to the I²C interface where I2C\_SCL, I2C\_SDA and PIO[2] are connected to the external EEPROM. The PIO[2] pin supplies the power to the EEPROM supply pin, e.g. VDD. At bootup, if there is no valid ROM image in the CSR1013 WLCSP ROM area the CSR1013 WLCSP tries to boot from the I²C interface, see Figure 6.5. This involves reading the code from the external EEPROM and loading it into the internal CSR1013 WLCSP RAM.

G-TW-0005553.1.1

Figure 6.1: Example of an I<sup>2</sup>C Interface EEPROM Connection

### Standard Mode 100 kHz

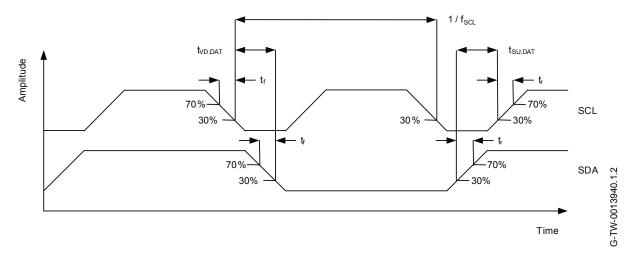

Figure 6.2 shows I<sup>2</sup>C standard mode 100 kHz timing diagram.

Figure 6.2: I<sup>2</sup>C Standard Mode 100 kHz Timing Diagram (Top Line: SCL, Bottom Line: SDA)

Table 6.2 lists I<sup>2</sup>C standard mode 100 kHz timing definition.

| Parameter                   | Symbol              | Min  | Max  | Unit |

|-----------------------------|---------------------|------|------|------|

| Clock Rate                  | f <sub>SCL</sub>    | -    | 100  | kHz  |

| SCL: Rise-time (30% to 70%) | t <sub>r</sub>      | -    | 50.3 | ns   |

| SCL: Fall-time (70% to 30%) | t <sub>f</sub>      | -    | 0.9  | ns   |

| SDA: Rise-time (30% to 70%) | t <sub>r</sub>      | -    | 55.3 | ns   |

| SDA: Fall-time (70% to 30%) | t <sub>f</sub>      | -    | 0.7  | ns   |

| Data set-up time            | t <sub>SU;DAT</sub> | 2511 | -    | ns   |

| Data valid time             | t <sub>VD;DAT</sub> | -    | 2.5  | μѕ   |

Table 6.2: I<sup>2</sup>C Standard Mode 100 kHz Timing Definition

#### Fast Mode 400 kHz

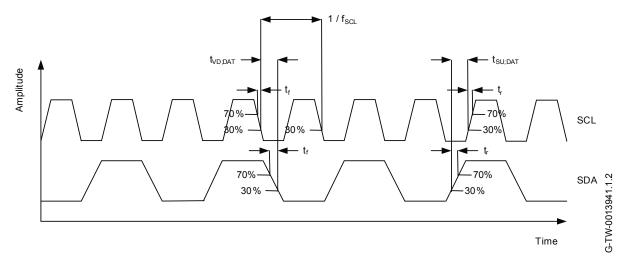

Figure 6.3 shows I<sup>2</sup>C fast mode 400 kHz timing diagram.

Figure 6.3: I<sup>2</sup>C Fast Mode 400 kHz Timing Diagram (Top Line: SCL, Bottom Line: SDA)

Table 6.3 lists I<sup>2</sup>C fast mode 400 kHz timing definition.

| Parameter                   | Symbol              | Min  | Мах  | Unit |

|-----------------------------|---------------------|------|------|------|

| Clock Rate                  | f <sub>SCL</sub>    | -    | 400  | kHz  |

| SCL: Rise-time (30% to 70%) | t <sub>r</sub>      | 41.4 | 50.6 | ns   |

| SCL: Fall-time (70% to 30%) | t <sub>f</sub>      | 0.7  | 0.9  | ns   |

| SDA: Rise-time (30% to 70%) | t <sub>r</sub>      | 46.0 | 55.9 | ns   |

| SDA: Fall-time (70% to 30%) | t <sub>f</sub>      | 0.5  | 0.7  | ns   |

| Data set-up time            | t <sub>SU;DAT</sub> | 573  | -    | ns   |

| Data valid time             | t <sub>VD;DAT</sub> | -    | 0.56 | μs   |

Table 6.3: I<sup>2</sup>C Fast Mode 400 kHz Timing Definition

# 6.3 SPI Master Interface

The SPI master memory interface in the CSR1013 WLCSP is overlaid on the I<sup>2</sup>C interface and uses a further 3 PIOs for the extra pins, see Table 6.4.

| SPI Flash Interface | Pin     |

|---------------------|---------|

| Flash_VDD           | PIO[2]  |

| SF_DIN              | PIO[3]  |

| SF_CS#              | PIO[4]  |

| SF_CLK              | I2C_SCL |

| SF_DOUT             | I2C_SDA |

Table 6.4: SPI Master Serial Flash Memory Interface

#### Note:

If an application using CSR1013 WLCSP is designed to boot from SPI serial flash, it is possible for the firmware to map the  $I^2C$  interface to alternative PIOs.

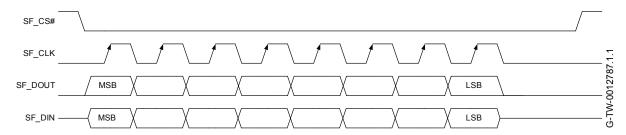

Figure 6.4 shows simple SPI timing diagram.

Figure 6.4: SPI Timing Diagram

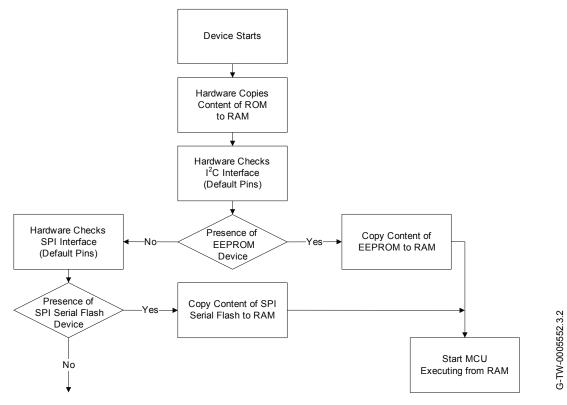

The boot-up sequence for CSR1013 WLCSP is controlled by hardware and firmware. Figure 6.5 shows the sequence of loading RAM with content from RAM, EEPROM and SPI serial flash.

Figure 6.5: Memory Boot-up Sequence

# 6.4 Programming and Debug Interface

#### Important Note:

The CSR1013 WLCSP debug SPI interface is available in SPI slave mode to enable an external MCU to program and control the CSR1013 WLCSP, generally via libraries or tools supplied by CSR. The protocol of this interface is proprietary. The 4 SPI debug lines directly support this function.

The SPI programs, configures and debugs the CSR1013 WLCSP. It is required in production. Ensure the 4 SPI signals are brought out to either test points or a header.

Take SPI\_PIO#\_SEL high to enable the SPI debug feature on PIO[8:5].

CSR1013 WLCSP uses a 16-bit data and 16-bit address programming and debug interface. Transactions occur when the internal processor is running or is stopped.

Data is written or read one word at a time. Alternatively, the auto-increment feature is available for block access.

### 6.4.1 Instruction Cycle

The CSR1013 WLCSP is the slave and receives commands on DEBUG\_MOSI and outputs data on DEBUG\_MISO. Table 6.5 shows the instruction cycle for a SPI transaction.

| 1 | Reset the SPI interface  | Hold DEBUG_CS# high for 2 DEBUG_CLK cycles        |

|---|--------------------------|---------------------------------------------------|

| 2 | Write the command word   | Take DEBUG_CS# low and clock in the 8-bit command |

| 3 | Write the address        | Clock in the 16-bit address word                  |

| 4 | Write or read data words | Clock in or out 16-bit data word(s)               |

| 5 | Termination              | Take DEBUG_CS# high                               |

Table 6.5: Instruction Cycle for a SPI Transaction

With the exception of reset, DEBUG\_CS# must be held low during the transaction. Data on DEBUG\_MOSI is clocked into the CSR1013 WLCSP on the rising edge of the clock line DEBUG\_CLK. When reading, CSR1013 WLCSP replies to the master on DEBUG\_MISO with the data changing on the falling edge of the DEBUG\_CLK. The master provides the clock on DEBUG\_CLK. The transaction is terminated by taking DEBUG\_CS# high.

The auto increment operation on the CSR1013 WLCSP cuts down on the overhead of sending a command word and the address of a register for each read or write, especially when large amounts of data are to be transferred. The auto increment offers increased data transfer efficiency on the CSR1013 WLCSP. To invoke auto increment, DEBUG\_CS# is kept low, which auto increments the address, while providing an extra 16 clock cycles for each extra word written or read.

### 6.4.2 Multi-slave Operation

Do not connect the CSR1013 WLCSP in a multi-slave arrangement by simple parallel connection of slave MISO lines. When CSR1013 WLCSP is deselected (DEBUG\_CS# = 1), the DEBUG\_MISO line does not float. Instead, CSR1013 WLCSP outputs 0 if the processor is running or 1 if it is stopped.

# 7 Power Control and Regulation

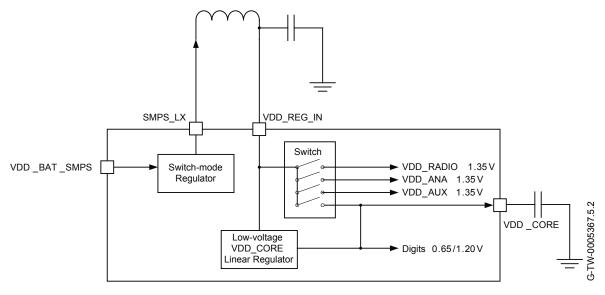

CSR1013 WLCSP contains 2 regulators:

- 1 switch-mode regulator, which generates the main supply rail from the battery

- 1 low-voltage linear regulator

Figure 7.1 shows the configuration for the power control and regulation with the CSR1013 WLCSP.

Figure 7.1: Voltage Regulator Configuration

# 7.1 Switch-mode Regulator

The switch-mode regulator generates the main rail from the battery supply, VDD\_BAT\_SMPS. The main rail supplies the lower regulated voltage to a further digital linear regulator and also to the analogue sections of the CSR1013 WLCSP.

The switch-mode regulator generates typically 1.35V.

# 7.2 Low-voltage VDD\_CORE Linear Regulator

The integrated low-voltage VDD\_CORE linear regulator powers the CSR1013 WLCSP digital circuits. The input voltage range is 0.65V to 1.35V. It can supply programmable voltages of 0.65V to 1.20V to the digital area of the CSR1013 WLCSP. The maximum output current for this regulator is 30mA.

Connect a minimum 470nF low ESR capacitor, e.g. MLC, to the VDD\_CORE output pin. Software controls the output voltage.

#### Important Note:

This regulator is only for CSR internal use. Section 8 shows CSR's recommended circuit connection.

### 7.3 Reset

CSR1013 WLCSP is reset by:

- Power-on reset

- Software-configured watchdog timer

#### 7.3.1 Digital Pin States on Reset

Table 7.1 shows the pin states of CSR1013 WLCSP on reset. PU and PD default to weak values unless specified otherwise.

| Pin Name / Group | On Reset  |

|------------------|-----------|

| I2C_SDA          | Strong PU |

| I2C_SCL          | Strong PU |

| PIO[11:0]        | Weak PD   |

| AIO[2:0]         | Weak PU   |

Table 7.1: Pin States on Reset

## 7.3.2 Power-on Reset

Table 7.2 shows how the power-on reset occurs.

| Power-on Reset                                | Тур  | Unit |

|-----------------------------------------------|------|------|

| Reset release on VDD_CORE rising              | 1.05 |      |

| Reset assert on VDD_CORE falling              | 1.00 | V    |

| Reset assert on VDD_CORE falling (Sleep mode) | 0.60 |      |

| Hysteresis                                    | 50   | mV   |

Table 7.2: Power-on Reset

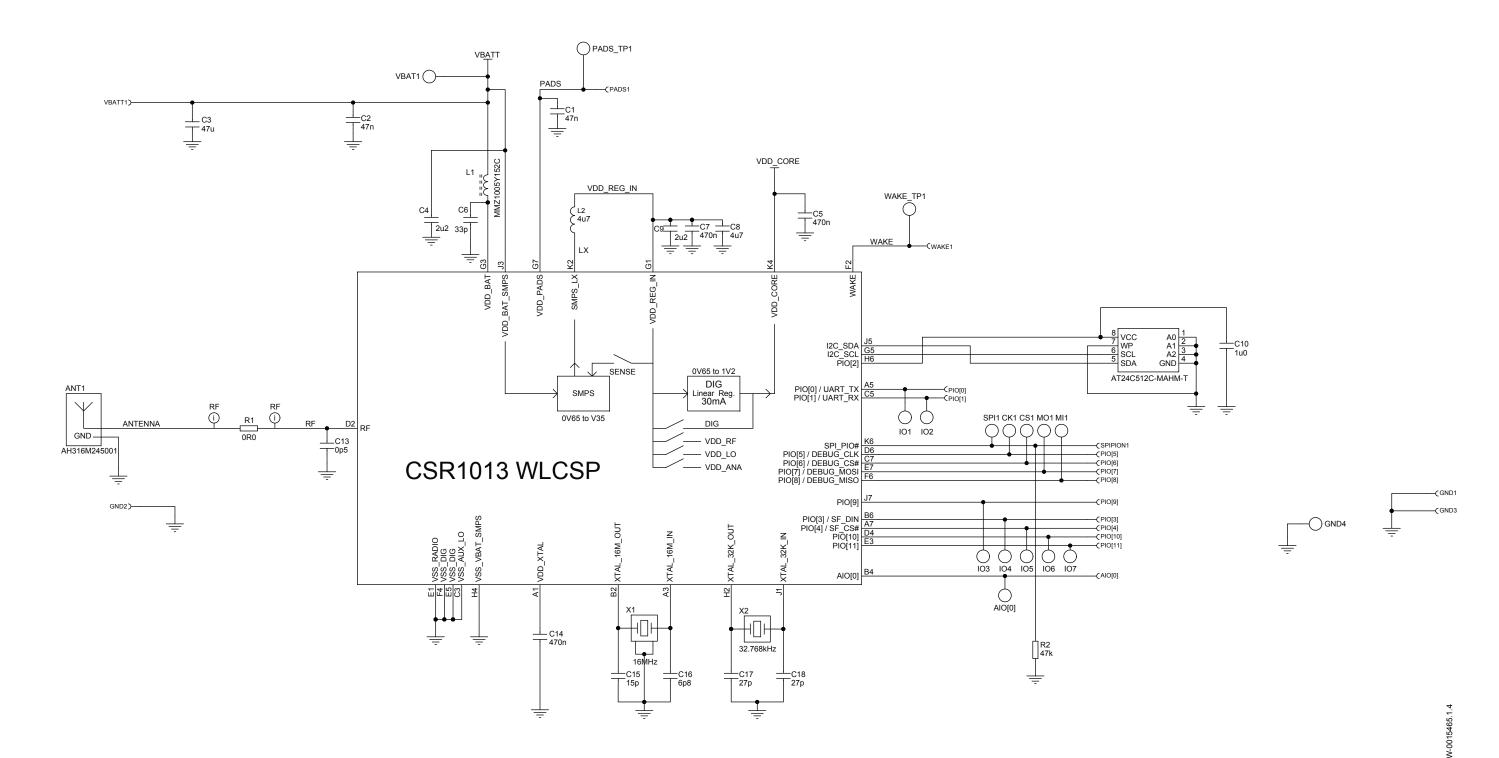

# 8 Example Application Schematic

# 9 Electrical Characteristics

# 9.1 Absolute Maximum Ratings

| Rating                                 | Min       | Max       | Unit |

|----------------------------------------|-----------|-----------|------|

| Storage temperature                    | -40       | 85        | °C   |

| Battery (VDD_BAT) operation            | 1.8       | 4.4       | V    |

| I/O supply voltage                     | -0.4      | 4.4       | V    |

| Other terminal voltages <sup>(a)</sup> | VSS - 0.4 | VDD + 0.4 | V    |

<sup>(</sup>a) VDD = Terminal Supply Domain

# 9.2 Recommended Operating Conditions

| Operating Condition                            | Min | Тур | Max | Unit |

|------------------------------------------------|-----|-----|-----|------|

| Operating temperature range                    | -30 | -   | 85  | °C   |

| Battery (VDD_BAT) operation <sup>(a) (b)</sup> | 1.8 | -   | 3.6 | V    |

| I/O supply voltage (VDD_PADS)(c)               | 1.2 | -   | 3.6 | V    |

<sup>(</sup>a) CSR1013 WLCSP is reliable and qualifiable to 4.3V (idle, active and deep sleep modes) and 3.8V (all modes), but there are minor deviations in performance relative to published performance values for 1.8V to 3.6V. For layout guidelines for 4.3V operation, see *CSR1013 Hardware Design Review Template*.

<sup>(</sup>b) For hibernate and dormant mode, see Customer Advisory: Use of CSR101x at Operating Voltages Above 3.6V.

$<sup>^{(</sup>c)}$  Safe to 4.3V if VDD\_BAT = 4.3V.

# 9.3 Input/Output Terminal Characteristics

## 9.3.1 Switch-mode Regulator

| Switch-mode Regulator                                       | Min  | Тур  | Max | Unit   |

|-------------------------------------------------------------|------|------|-----|--------|

| Input voltage <sup>(a)</sup>                                | 1.8  | -    | 3.6 | V      |

| Output voltage <sup>(b)</sup>                               | -    | 1.35 | -   | V      |

| Temperature coefficient                                     | -200 | -    | 200 | ppm/°C |

| Normal Operation                                            |      |      |     |        |

| Output noise, frequency range 100Hz to 100kHz               | -    | -    | 0.4 | mV rms |

| Settling time, settling to within 10% of final value        | -    | -    | 30  | μs     |

| Output current (I <sub>max</sub> )                          | -    | -    | 50  | mA     |

| Quiescent current (excluding load, I <sub>load</sub> < 1mA) | -    | -    | 20  | μA     |

| Ultra Low-power Mode                                        |      |      |     |        |

| Output current (I <sub>max</sub> )                          | -    | -    | 100 | μA     |

| Quiescent current                                           | -    | -    | 1   | μA     |

<sup>(</sup>a) CSR1013 WLCSP is reliable and qualifiable to 4.3V (idle, active and deep sleep modes) and 3.8V (all modes), but there are minor deviations in performance relative to published performance values for 1.8V to 3.6V. For layout guidelines for 4.3V operation, see *CSR1013 Hardware Design Review Template*.

## 9.3.2 Low-voltage Linear Regulator

| Normal Operation | Min  | Тур | Max  | Unit |

|------------------|------|-----|------|------|

| Input voltage    | 0.65 | -   | 1.35 | V    |

| Output voltage   | 0.65 | -   | 1.20 | V    |

#### Important Note:

This regulator is only for CSR internal use. Section 8 shows CSR's recommended circuit connection.

### 9.3.3 Digital Terminals

| Input Voltage Levels                   | Min               | Тур | Max               | Unit |

|----------------------------------------|-------------------|-----|-------------------|------|

| V <sub>IL</sub> input logic level low  | -0.4              | -   | 0.3 x<br>VDD_PADS | V    |

| V <sub>IH</sub> input logic level high | 0.7 x<br>VDD_PADS | -   | VDD_PADS + 0.4    | V    |

| T,/T <sub>f</sub>                      | -                 | -   | 25                | ns   |

<sup>(</sup>b) During Run mode, see Section 4.1.

| Output Voltage Levels                                             | Min                | Тур | Max | Unit |

|-------------------------------------------------------------------|--------------------|-----|-----|------|

| V <sub>OL</sub> output logic level low, l <sub>OL</sub> = 4.0mA   | -                  | -   | 0.4 | V    |

| V <sub>OH</sub> output logic level high, I <sub>OH</sub> = -4.0mA | 0.75 x<br>VDD_PADS | -   | -   | V    |

| T <sub>r</sub> /T <sub>f</sub>                                    | -                  | -   | 5   | ns   |

| Input, Output and Tristate Currents <sup>(a)</sup>       | Min  | Тур  | Max   | Unit |

|----------------------------------------------------------|------|------|-------|------|

| I <sub>OL</sub> output current low, V <sub>OL</sub> max  | -    | 8    | 10    | mA   |

| I <sub>OH</sub> output current high, V <sub>OH</sub> min | -    | 8    | 10    | mA   |

| With strong pull-up                                      | -150 | -40  | -10   | μА   |

| I <sup>2</sup> C with strong pull-up                     | -250 | -    | -     | μA   |

| With strong pull-down                                    | 10   | 40   | 150   | μA   |

| With weak pull-up                                        | -5.0 | -1.0 | -0.33 | μA   |

| With weak pull-down                                      | 0.33 | 1.0  | 5.0   | μΑ   |

| C <sub>I</sub> input capacitance                         | 1.0  | -    | 5.0   | pF   |

$<sup>^{</sup>m (a)}$  Maximum current draw from VDD\_PADS is less than 30mA depending on board design.

### 9.3.4 AIO

| Input/Output Voltage Levels | Min | Тур | Max     | Unit |

|-----------------------------|-----|-----|---------|------|

| Input voltage               | 0   | -   | VDD_AUX | V    |

| Output voltage              | 0   | -   | VDD_AUX | V    |

| Output drive strength       | -   | 4   | -       | mA   |

# 9.3.4.1 Auxiliary ADC

| Auxiliary ADC                      |     | Min | Тур | Max     | Unit |

|------------------------------------|-----|-----|-----|---------|------|

| Resolution                         |     | -   | -   | 10      | Bits |

| Input voltage range <sup>(a)</sup> |     | 0   | -   | VDD_AUX | V    |

| Accuracy                           | INL | -3  | -   | 3       | LSB  |

|                                    | DNL | -3  | -   | 3       | LSB  |

| Auxiliary ADC                             | Min  | Тур | Max   | Unit      |

|-------------------------------------------|------|-----|-------|-----------|

| Offset                                    | -1   | -   | 1     | LSB       |

| Gain error                                | -0.8 | -   | 0.8   | %         |

| Input bandwidth                           | -    | 100 | -     | kHz       |

| Conversion time (measured at application) | -    | 46  | -     | μs        |

| Sample rate <sup>(b)</sup>                | -    | -   | 21000 | Samples/s |

| ADC block conversion current              | -    | 410 | -     | μΑ        |

<sup>(</sup>a) LSB size = VDD\_AUX/1023

#### 9.3.4.2 Auxiliary DAC

| Auxiliary DAC             | Min   | Тур  | Max     | Unit |

|---------------------------|-------|------|---------|------|

| Resolution                | -     | -    | 10      | Bits |

| Supply voltage, VDD_ANA   | 1.30  | 1.35 | 1.40    | V    |

| Output voltage range      | 0     | -    | VDD_AUX | V    |

| Full-scale output voltage | 1.30  | 1.35 | 1.40    | V    |

| LSB size                  | 0     | 1.32 | 2.64    | mV   |

| Offset                    | -1.32 | 0    | 1.32    | mV   |

| Integral non-linearity    | -3    | 0    | 3       | LSB  |

| Settling time             | -     | -    | 250     | ns   |

#### Important Note:

Access to the auxiliary DAC is firmware-dependent, for more information about its availability contact CSR.

<sup>(</sup>b) The auxiliary ADC is accessed through the firmware API. The sample rate given is achieved as part of this function.

## 9.4 Junction Temperature

Table 9.1 lists the junction temperature when the device is operating within recommended operating conditions.

| Parameter            | Min | Тур | Max | Unit |

|----------------------|-----|-----|-----|------|

| Junction temperature | -   | -   | 125 | °C   |

Table 9.1: Junction Temperature within Recommended Operating Conditions

## 9.5 ESD Protection

Apply ESD static handling precautions during manufacturing.

Table 9.2 shows the ESD handling maximum ratings.

| Condition                                                        | Class | Max Rating       |

|------------------------------------------------------------------|-------|------------------|

| Charged Device Model Contact Discharge per JEDEC EIA/JESD22-C101 | C2    | 1000V (all pins) |

Table 9.2: ESD Handling Ratings

# 10 Current Consumption

Table 10.1 shows CSR1013 WLCSP total typical current consumption measured at the battery.

| Mode       | Description                                                                                                                               | Total Typical Current at 3.0V |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Dormant    | All functions are shut down. To wake them up, toggle the WAKE pin.                                                                        | <900nA                        |

| Hibernate  | VDD_PADS = OFF, REFCLK = OFF, SLEEPCLK = ON, VDD_BAT = ON                                                                                 | <1.9µA                        |

| Deep sleep | VDD_PADS = ON, REFCLK = OFF, SLEEPCLK = ON, VDD_BAT = ON, RAM = ON, digital circuits = ON, SMPS = ON (low-power mode), 2.2ms wake-up time | <5μΑ                          |

| Idle       | VDD_PADS = ON, REFCLK = ON, SLEEPCLK = ON, VDD_BAT = ON, RAM = ON, digital circuits = ON, MCU = IDLE, <1µs wake-up time                   | ~1mA                          |

| RX active  | -                                                                                                                                         | ~20mA @ 3.0V peak current     |

| TX active  | -                                                                                                                                         | ~18mA @ 3.0V peak current     |

Table 10.1: Current Consumption

#### Note:

Current consumption measurements were made:

- At 20°C and with 3.0V VBAT.

- For the whole chip: including radio, microcontroller and necessary peripherals.

- Using SDK 2.4.3.

## 11 CSR Green Semiconductor Products and RoHS Compliance

CSR confirms that CSR Green semiconductor products comply with the following regulatory requirements:

- Restriction of Hazardous Substances directive guidelines in the EU RoHS Directive 2011/65/EU<sup>1</sup>.

- EU REACH, Regulation (EC) No 1907/2006<sup>1</sup>:

- List of substances subject to authorisation (Annex XIV)

- Restrictions on the manufacture, placing on the market and use of certain dangerous substances, preparations and articles (Annex XVII). This Annex now includes requirements that were contained within EU Directive, 76/769/EEC. There are many substance restrictions within this Annex, including, but not limited to, the control of use of Perfluorooctane sulfonates (PFOS).

- When requested by customers, notification of substances identified on the Candidate List as Substances of Very High Concern (SVHC)<sup>1</sup>.

- POP regulation (EC) No 850/2004<sup>1</sup>

- EU Packaging and Packaging Waste, Directive 94/62/EC<sup>1</sup>

- Montreal Protocol on substances that deplete the ozone layer.

- Conflict minerals, Section 1502, Dodd-Frank Wall Street Reform and Consumer Protection act, which affects columbite-tantalite (coltan / tantalum), cassiterite (tin), gold, wolframite (tungsten) or their derivatives. CSR is a fabless semiconductor company: all manufacturing is performed by key suppliers. CSR have mandated that the suppliers shall not use materials that are sourced from "conflict zone mines" but understand that this requires accurate data from the EICC programme. CSR shall provide a complete EICC / GeSI template upon request.

CSR has defined the "CSR Green" standard based on current regulatory and customer requirements including free from bromine, chlorine and antimony trioxide.

Products and shipment packaging are marked and labelled with applicable environmental marking symbols in accordance with relevant regulatory requirements.

This identifies the main environmental compliance regulatory restrictions CSR specify. For more information on the full "CSR Green" standard, contact product.compliance@csr.com.

Including applicable amendments to EU law which are published in the EU Official Journal, or SVHC Candidate List updates published by the European Chemicals Agency (ECHA).

## 12 CSR1013 WLCSP Software Stack

CSR1013 WLCSP is supplied with Bluetooth v4.1 specification compliant stack firmware. Figure 12.1 shows that the CSR1013 WLCSP software architecture enables the Bluetooth processing and the application program to run on the internal RISC MCU.

Figure 12.1: Software Architecture

# 13 Tape and Reel Information

For tape and reel packing and labelling see IC Packing and Labelling Specification.

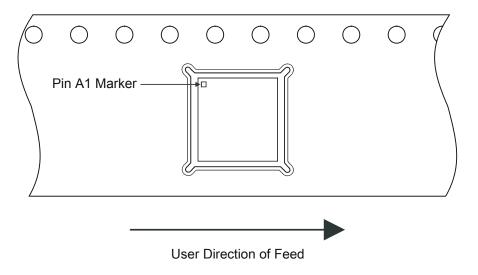

## 13.1 Tape Orientation

Figure 13.1 shows the CSR1013 WLCSP packing tape orientation.

Figure 13.1: Tape Orientation

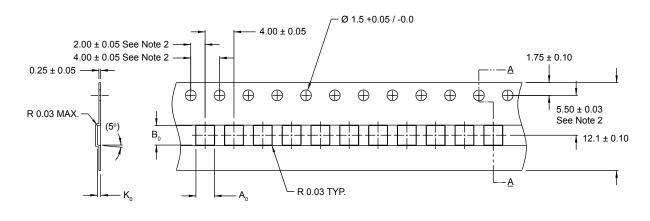

## 13.2 Tape Dimensions

Figure 13.2 shows the dimensions of the tape for the CSR1013 WLCSP.

Section A - A

G-TW-0014620.1.2

Figure 13.2: Tape Dimensions

| A <sub>0</sub> | B <sub>0</sub> | K <sub>0</sub> | Unit | Notes                                                                                                                                                                                                                                                                                                                                                       |

|----------------|----------------|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.55           | 2.70           | 0.45           | mm   | <ol> <li>1. 10 sprocket hole pitch cumulative tolerance ±0.1.</li> <li>2. Camber in compliance with EIA 763.</li> <li>3. Pocket position relative to sprocket hole measured as true position of pocket, not pocket hole.</li> <li>4. A<sub>0</sub> and B<sub>0</sub> are calculated on a plane at a distance "R" above the bottom of the pocket.</li> </ol> |

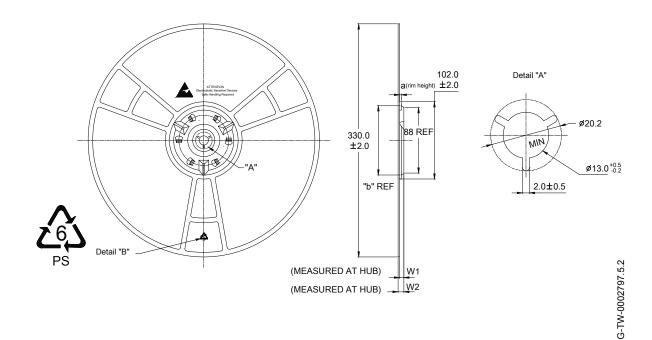

#### 13.3 Reel Information

Figure 13.3: Reel Dimensions

| Package Type                         | Nominal Hub Width<br>(Tape Width) | а   | b    | W1                 | W2 Max | Units |

|--------------------------------------|-----------------------------------|-----|------|--------------------|--------|-------|

| 2.43 x 2.56 x<br>0.35 mm<br>UT-WLCSP | 12                                | 4.5 | 98.0 | 12.4<br>(2.0/-0.0) | 18.4   | mm    |

## 13.4 Moisture Sensitivity Level

CSR1013 WLCSP is qualified to moisture sensitivity level MSL1 in accordance with JEDEC J-STD-020.

## 14 Document References

| Document                                                                                           | Reference, Date                                       |

|----------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Core Specification of the Bluetooth System.                                                        | Bluetooth Specification Version 4.1, 03 December 2013 |

| CSR1013 Hardware Design Review Template.                                                           | CS-330976-DD                                          |

| CSR1013 WLCSP (3.3V Operation) Performance<br>Specification .                                      | CS-332465-SP                                          |

| CSR1013 WLCSP (4.3V Operation) Performance<br>Specification .                                      | CS-332466-SP                                          |